Tese do PPGC-UFPel recebe o prêmio no 21st IEEE Latin-American Test Symposium

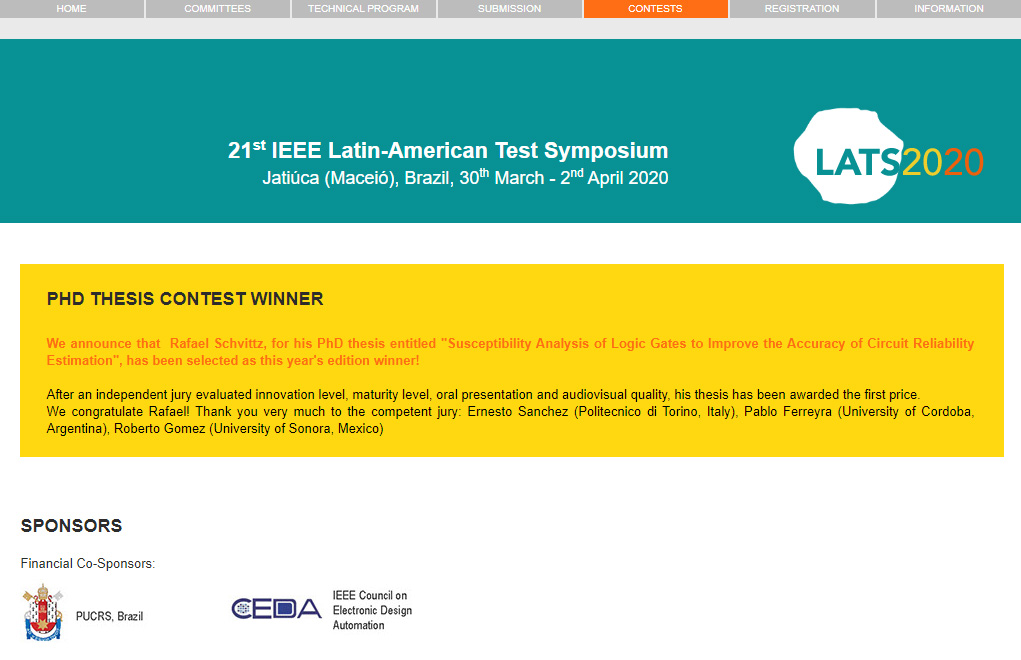

A tese de doutorado de Rafael Budim Schvittz, desenvolvida no Programa de Pós-graduação em Computação da UFPel, venceu o concurso de teses no 21st IEEE Latin-American Test Symposium, o maior e mais importante evento na área de Teste de Circuitos Integrados na América Latina.

O trabalho intitulado “Susceptibility Analysis of Logic Gates to Improve the Accuracy of Circuit Reliability Estimation”, orientado pelos professores Leomar Soares da Rosa Júnior (UFPel) e Paulo Francisco Butzen (UFRGS), concorreu com diversos trabalhos de doutorado desenvolvidos no exterior. A banca específica de avaliação, formada por pesquisadores internacionais da Politécnico de Torino (Itália), da Universidade de Córdoba (Argentina) e da Universidade de Sonora (México), divulgou o resultado durante este mês de maio.

Segundo o professor Leomar Rosa Júnior, esta é uma importante conquista para o PPGC da UFPel. “Vencer um concurso de expressão como este, em um simpósio internacional de grande visibilidade para a área de teste de circuitos integrados nos motiva a seguir em frente e continuar desenvolvendo pesquisas de ponta na universidade.”

O trabalho vencedor foi julgado considerando diversos quesitos, dentre eles, a capacidade de inovação, o nível de maturidade, os resultados obtidos e a qualidade da apresentação.

O professor Paulo Butzen complementa: “Este prêmio é reflexo da qualidade na pesquisa desenvolvida. A partir dos membros avaliadores e dos critérios avaliados, fica claro que o trabalho desenvolvido possui alto grau de inovação e seus resultados tem alcance internacional. O reconhecimento também reforça a importância da experiência interinstitucional como contribuinte para a disseminação e diversificação dos saberes”.

A tese desenvolvida na UFPel ataca um dos grandes desafios no desenvolvimento de circuitos digitais em tecnologia nanométrica, especificamente na área de confiabilidade. “Para lidar com os desafios da tecnologia nanométrica dos circuitos digitais, novas metodologias de projeto são necessárias de forma a aumentar a robustez destes circuitos. Devido aos custos associados com as técnicas de tolerância a falhas, soluções alternativas, baseadas em tolerância a falhas parcial e técnicas para ignorar as falhas estão sendo cada vez mais exploradas para o problema da confiabilidade. Nesse contexto, uma avaliação precisa da confiabilidade dos circuitos é fundamental para permitir um fluxo de projeto automatizado de avaliação de confiabilidade, no qual as ferramentas de síntese possam rapidamente alternar entre diversas configurações de circuitos para definir a melhor opção”, explica Rafael Schvittz.